# Charles University in Prague Faculty of Mathematics and Physics

# MASTER THESIS

# Michal Vaner

# Cache-oblivious Algorithms

Department of Applied Mathematics

Supervisor of the master thesis: Mgr. Martin Mareš Ph.D.

Study programme: Computer Science

Specialization: Discrete Models And Algorithms

Prague 2012

I would like to thank my supervisor Martin Mareš for his invaluable advice, questions and proof-reading the text. My parents and girlfriend Lucka also deserve my gratitude for their support and patience in times when I was busy working on the thesis. I should thank the Department of Applied Mathematics for providing me with the computers for running the benchmarks. And I shouldn't forget to mention my thanks to the computers in question (Kamenolom and Drahokam from the department and my Hydra), which spent a long time performing tedious computations for me. Finally, the work would not be possible without the good open source software available on the Internet, like latex or git and more.

| I declare that I carried out this master thesis independently, and only with the cited sources, literature and other professional sources.                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I understand that my work relates to the rights and obligations under the Act No. 121/2000 Coll., the Copyright Act, as amended, in particular the fact that the Charles University in Prague has the right to conclude a license agreement on the use of this work as a school work pursuant to Section 60 paragraph 1 of the Copyright Act. |

| In addition, I grant everybody the right to copy, distribute, transmit and make commercial use of the work under the Creative Commons Attribution-NoDerivs 3.0 Unported license (http://creativecommons.org/licenses/by-nd/3.0/).                                                                                                             |

| In Prague on 2012-04-10                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                               |

Název práce: Cache-oblivious Algoritmy

Autor: Bc. Michal Vaner

Katedra: Katedra aplikované matematiky

Vedoucí diplomové práce: Mgr. Martin Mareš, Ph.D., Katedra aplikované matematiky

Abstrakt: V této práci se zabýváme výpočetním modelem cache-oblivious algoritmů, který je inspirovaný chováním paměťové hierarchie současných počítačů. V tomto modelu studujeme některé grafové algoritmy a techniky jejich návrhu. Zabýváme se zejména procházením grafu, rozkladem na komponenty souvislosti a hledáni v inkluzi maximálního párování. Taktéž zkoumáme třídění a násobení matic jako podproblémy mnohých grafových algoritmů. Mimo dříve známých algoritmů uvádíme i několik nových. Jejich efektivitu posuzujeme jak asymptoticky, tak experimentálně na reálném hardwaru a srovnáváme je s klasickými algoritmy.

Klíčová slova: Algoritmus, cache-oblivious, výpočetní model, srovnávací test

Title: Cache-oblivious Algorithms

Author: Bc. Michal Vaner

Department: Department of Applied Mathematics

Supervisor: Mgr. Martin Mareš, Ph.D., Department of Applied Mathematics

Abstract: In this work, we study the cache-oblivious computation model, which is inspired by the behaviour of the memory hierarchy of current computers. We study several graph algorithms and techniques of their design in this model. We consider graph searching, identifying connected components and computing maximal matching. We also study sorting and matrix multiplication as subproblems of many graph algorithms. In addition to previously known algorithms, we present several new ones. We study their efficiency both by the means of asymptotic complexity and by benchmarking them on real hardware and we compare them with classical algorithms.

Keywords: Algorithm, cache-oblivious, computation model, benchmark

# Contents

| 1 Introduction |                               |                                          |    |  |  |  |

|----------------|-------------------------------|------------------------------------------|----|--|--|--|

| <b>2</b>       | Conventions and used notation |                                          |    |  |  |  |

|                | 2.1                           | Graphs                                   | 5  |  |  |  |

|                | 2.2                           | Cache and memory                         | 5  |  |  |  |

| 3              | Cor                           | putational models                        | 7  |  |  |  |

|                | 3.1                           | Real hardware                            | 7  |  |  |  |

|                | 3.2                           | RAM                                      | 8  |  |  |  |

|                | 3.3                           | I/O or Cache-aware                       | 9  |  |  |  |

|                | 3.4                           | Cache-oblivious                          | 10 |  |  |  |

|                | 3.5                           | Streaming model                          | 11 |  |  |  |

|                | 3.6                           | Parallel modifications                   | 11 |  |  |  |

| 4              | Ber                           | enchmarks                                |    |  |  |  |

|                | 4.1                           | Pointers and benchmark types             | 13 |  |  |  |

|                |                               | 4.1.1 Measuring runtime                  | 13 |  |  |  |

|                |                               | 4.1.2 Measuring LRU cache of disk        | 14 |  |  |  |

|                |                               | 4.1.3 Simulating cache behaviour         | 14 |  |  |  |

|                | 4.2                           | Inputs                                   | 15 |  |  |  |

|                |                               | 4.2.1 Sorting inputs                     | 15 |  |  |  |

|                |                               | 4.2.2 Matrix inputs                      | 15 |  |  |  |

|                |                               | 4.2.3 Graph inputs                       | 16 |  |  |  |

| 5              | Cor                           | mon techniques                           | 17 |  |  |  |

|                | 5.1                           | Algorithm approaches                     | 17 |  |  |  |

|                |                               | 5.1.1 Scans                              | 17 |  |  |  |

|                |                               | 5.1.2 Divide and conquer                 | 18 |  |  |  |

|                |                               | 5.1.3 Dividing vertices to conquer edges | 18 |  |  |  |

|                |                               | 5.1.4 Van Emde-Boas lavout               | 19 |  |  |  |

|   | 5.2                                                | Comn       | non lemmata               | . 20 |  |  |  |  |

|---|----------------------------------------------------|------------|---------------------------|------|--|--|--|--|

| 6 | Sor                                                | Sorting 23 |                           |      |  |  |  |  |

|   | 6.1                                                | Merge      | e sort                    | . 23 |  |  |  |  |

|   |                                                    | 6.1.1      | Layered                   | . 24 |  |  |  |  |

|   |                                                    | 6.1.2      | Recursive                 | . 24 |  |  |  |  |

|   | 6.2                                                | Quick      | sort                      | . 25 |  |  |  |  |

|   | 6.3                                                | Funne      | el sort                   | . 27 |  |  |  |  |

|   |                                                    | 6.3.1      | Funnel                    | . 27 |  |  |  |  |

|   |                                                    | 6.3.2      | Estimates                 | . 29 |  |  |  |  |

|   | 6.4                                                | Exper      | rimental results          | . 31 |  |  |  |  |

| 7 | Matrices 37                                        |            |                           |      |  |  |  |  |

|   | 7.1                                                | Straig     | ghtforward multiplication | . 37 |  |  |  |  |

|   | 7.2                                                | Divide     | e and conquer             | . 38 |  |  |  |  |

|   | 7.3                                                | The Z      | Z representation          | . 40 |  |  |  |  |

|   | 7.4                                                | Strass     | sen's algorithm           | . 41 |  |  |  |  |

|   | 7.5                                                | Exper      | rimental results          | . 42 |  |  |  |  |

| 8 | Toolbox of graph algorithms and data structures 45 |            |                           |      |  |  |  |  |

|   | 8.1                                                | Buffer     | r repository tree         | . 45 |  |  |  |  |

|   | 8.2                                                | Buffer     | r priority tree           | . 47 |  |  |  |  |

|   | 8.3                                                | Searches   |                           |      |  |  |  |  |

|   |                                                    | 8.3.1      | BFS for undirected graphs | . 51 |  |  |  |  |

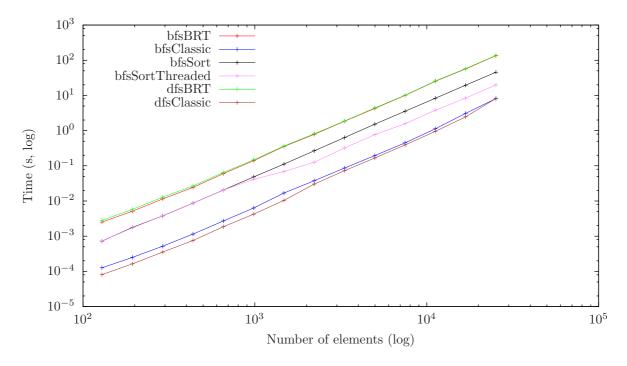

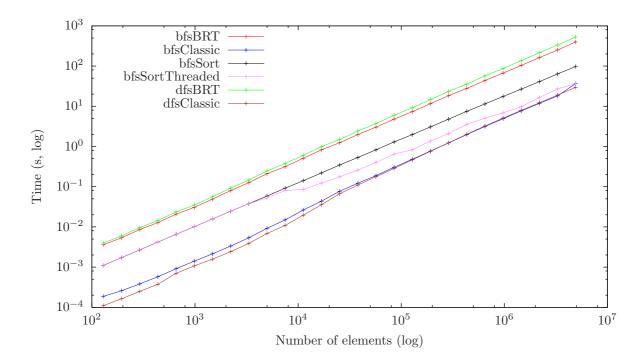

|   |                                                    | 8.3.2      | Experimental results      | . 53 |  |  |  |  |

| 9 | Components 57                                      |            |                           |      |  |  |  |  |

|   | 9.1                                                | BFS        |                           |      |  |  |  |  |

|   | 9.2                                                | Divide     | e and conquer             | . 57 |  |  |  |  |

|   |                                                    | 9.2.1      | Overview                  | . 57 |  |  |  |  |

|   |                                                    | 9.2.2      | Technical details         | . 58 |  |  |  |  |

|   |                                                    | 9.2.3      | Trivial subproblem        | . 60 |  |  |  |  |

|   |                                                    | 9.2.4      | Correctness               | . 60 |  |  |  |  |

|              |       | 9.2.5            | In-place implementation      | 62  |

|--------------|-------|------------------|------------------------------|-----|

|              |       | 9.2.6            | Analysis of complexity       | 63  |

|              |       | 9.2.7            | Comparison                   | 65  |

|              | 9.3   | Reacha           | ability                      | 65  |

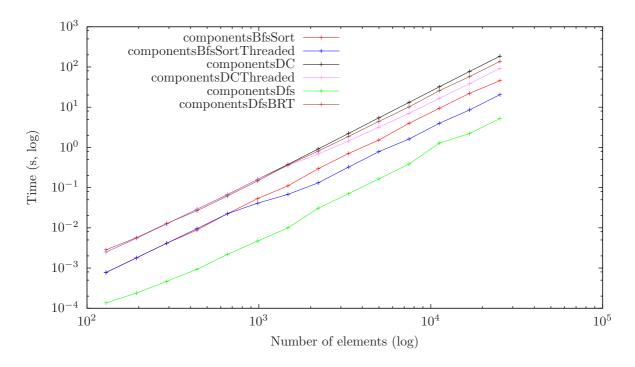

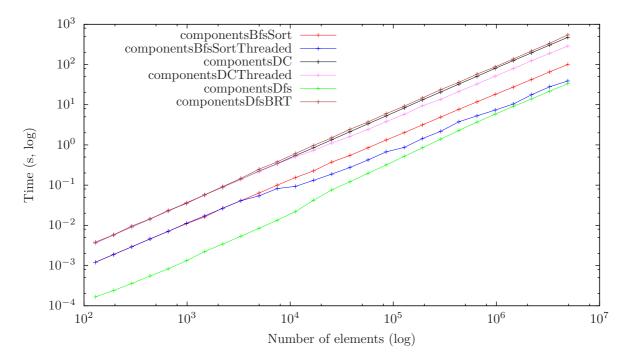

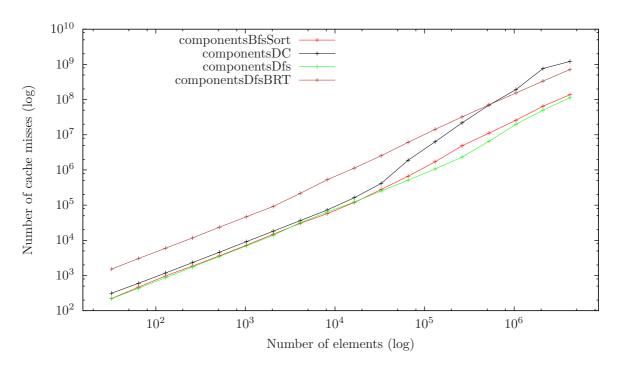

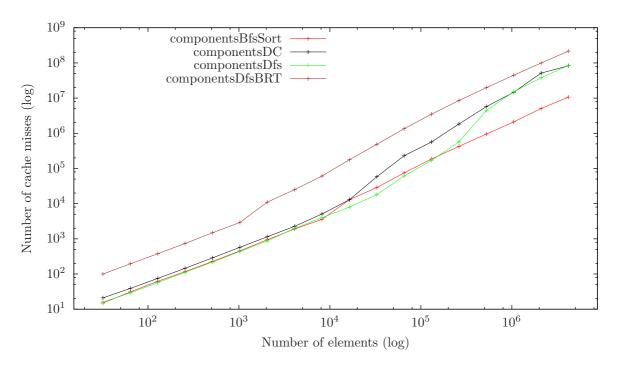

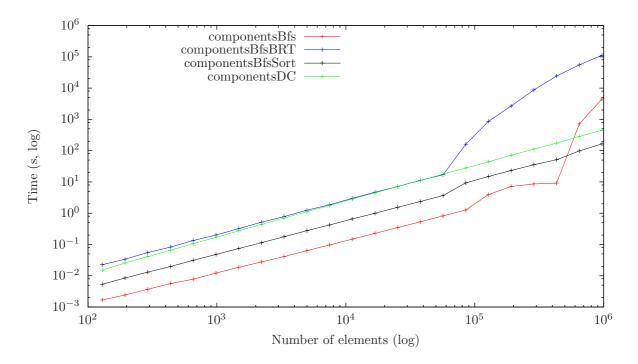

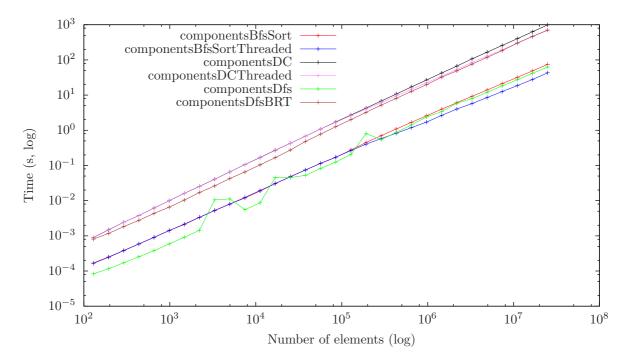

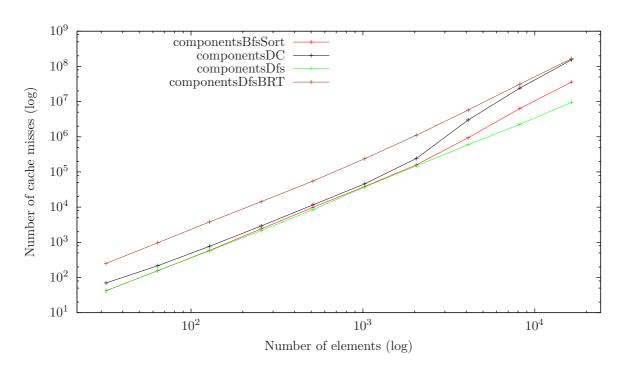

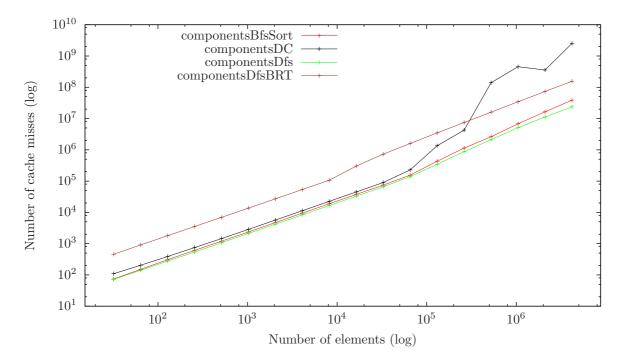

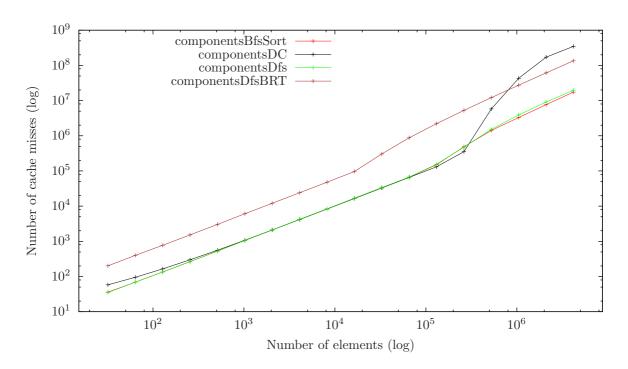

|              | 9.4   | Experi           | imental results              | 67  |

| 10           | Max   | kimal r          | natching                     | 71  |

|              | 10.1  | RAM a            | approach                     | 71  |

|              | 10.2  | With I           | BRT                          | 71  |

|              | 10.3  | Divide           | and Conquer                  | 74  |

|              |       | 10.3.1           | Overview                     | 74  |

|              |       | 10.3.2           | Implementation details       | 75  |

|              |       | 10.3.3           | Correctness and complexities | 75  |

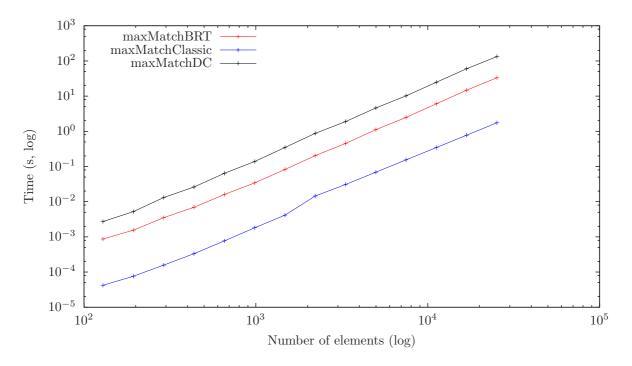

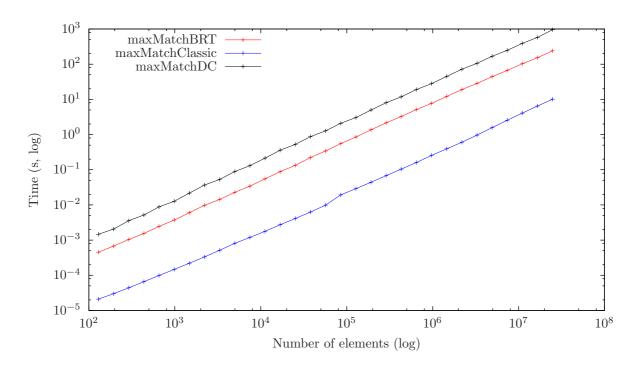

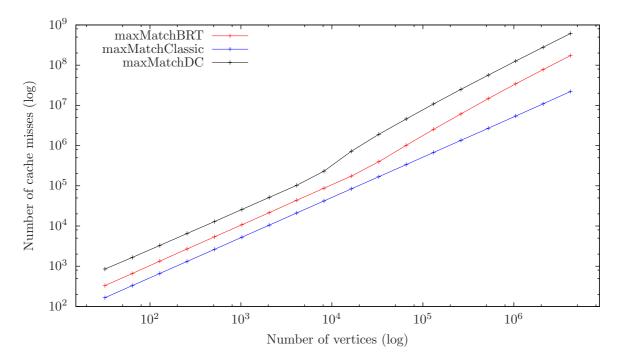

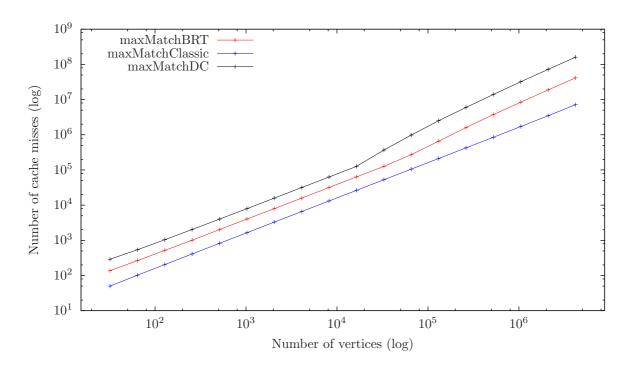

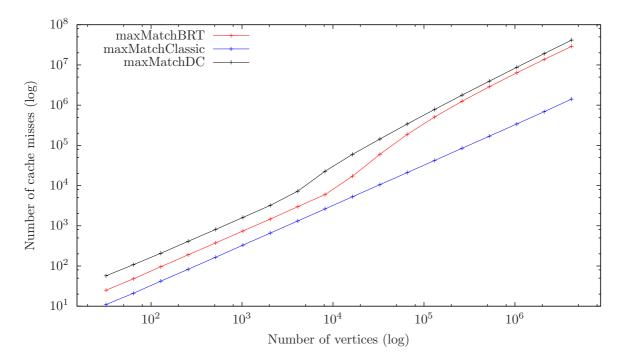

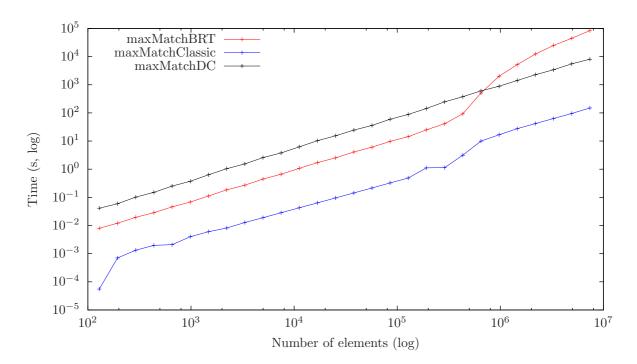

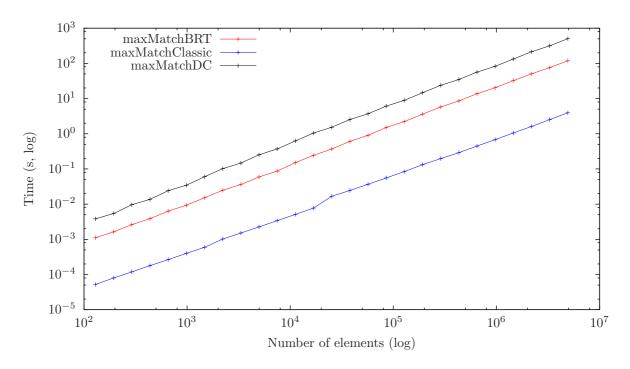

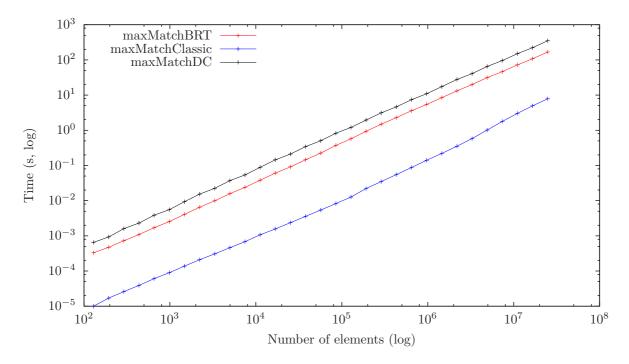

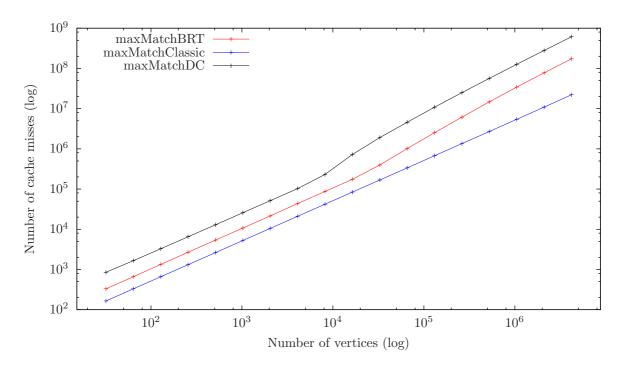

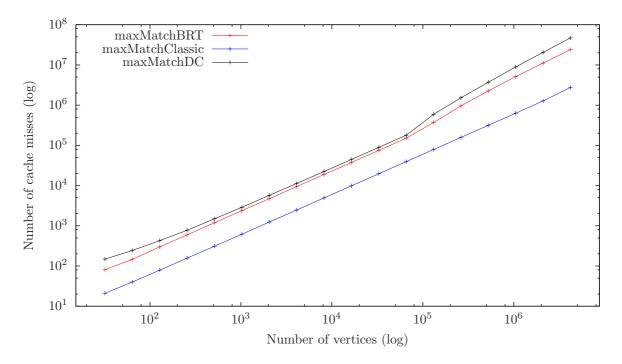

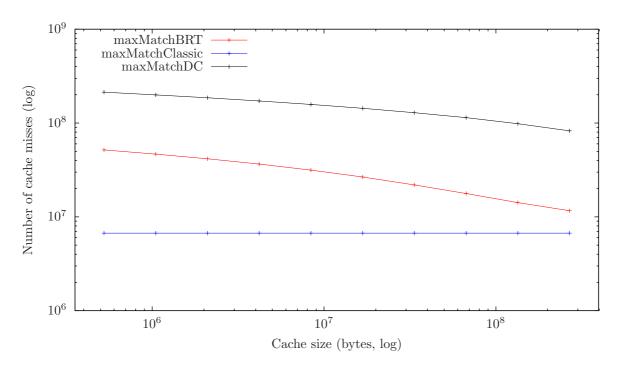

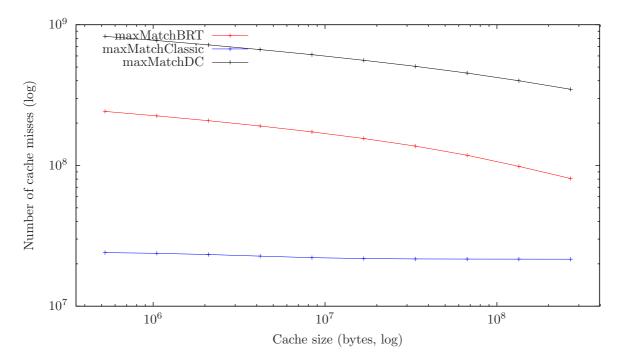

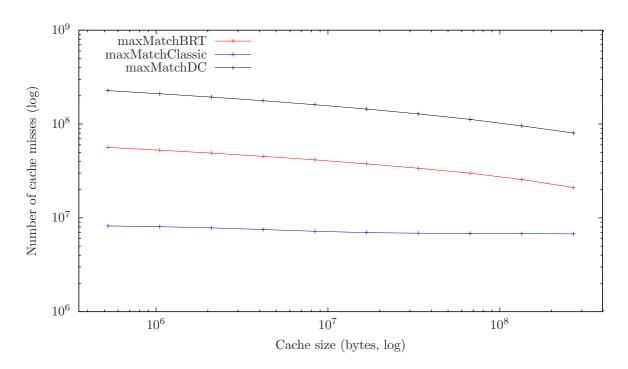

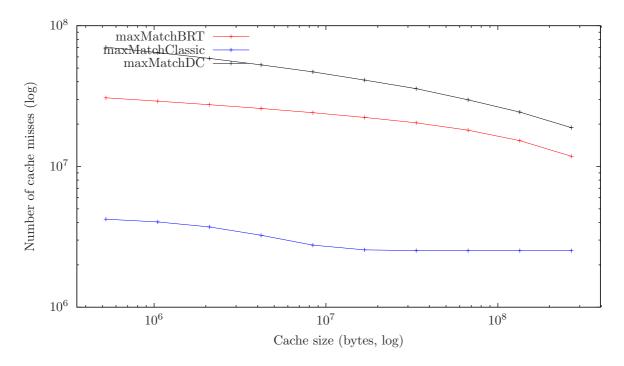

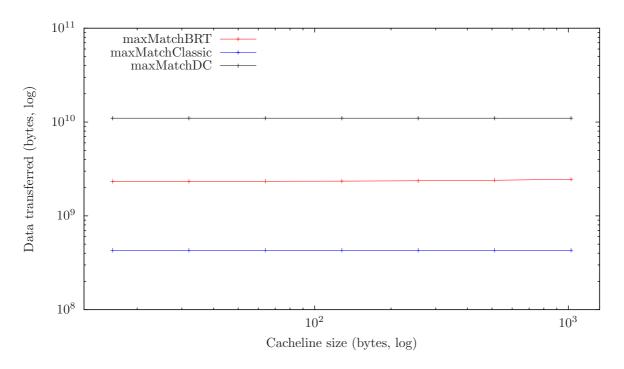

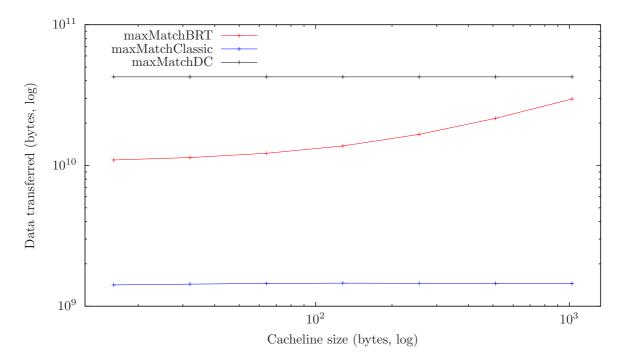

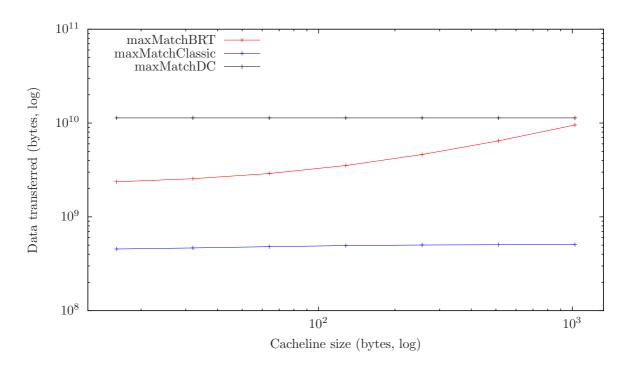

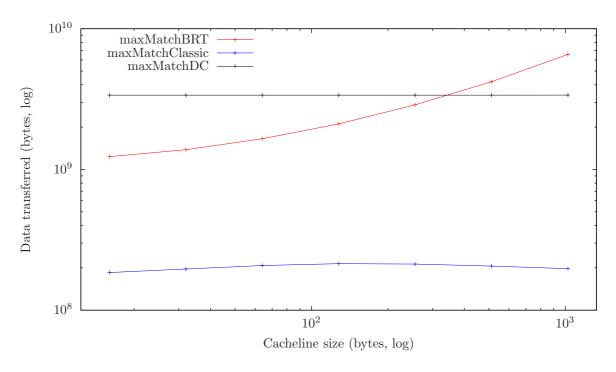

|              | 10.4  | Experi           | imental results              | 77  |

| 11           | Con   | clusion          | ns                           | 83  |

| Bi           | bliog | raphy            |                              | 85  |

| Li           | st of | $Figur \epsilon$ | es                           | 87  |

| $\mathbf{A}$ | Furt  | her gr           | raphs of experiments         | 89  |

|              | A.1   | Sorting          | 9                            | 89  |

|              | A.2   | Matrix           | multiplication               | 93  |

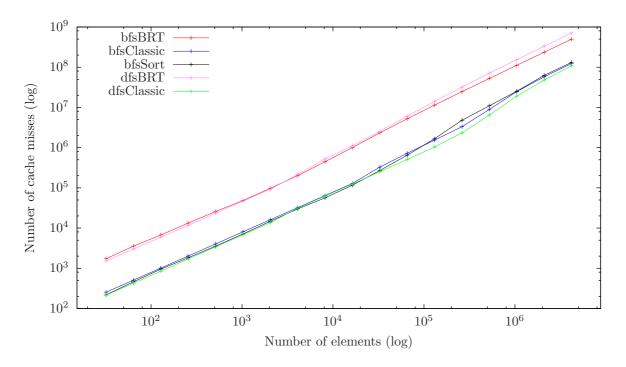

|              | A.3   | Graph            | searching                    | 93  |

|              | A.4   | Compo            | onents                       | 95  |

|              | A 5   | Maxim            | nal matching                 | 103 |

# 1. Introduction

In the recent years, the processor speed increased vastly. Manufacturing memory with corresponding speeds would be very expensive if not impossible. Therefore memory caches were inserted between the main memory and the processor. These caches are faster than the main memory, but also smaller. A cache keeps copy of some of the data from the main memory which were accessed recently. This is because many algorithms often access the same data many times and the cache then can provide it faster.

While the effect of cache is generally good on any algorithm, the speedup is different for different algorithms. Some patterns of memory accesses utilize the cache better than others. A typical example of this effect is traversing elements of a matrix. As we show below, traversing a row of a square matrix is much faster than traversing its column.

Algorithms that are aware of the cache and use it optimally were created. Programs using these algorithms are however written for specific parameters of the cache, which makes them less portable. Fortunately, it was discovered [1] that there are algorithms which use the cache optimally up to multiplicative constants without knowledge of the cache parameters. Such algorithms are called cache-oblivious. Their advantage is that they work optimally with caches of any size. Sometimes a simple modification of a classical algorithm makes it cache-oblivious, many algorithms are based on less straightforward ideas.

We study cache-oblivious algorithms for some graph problems and their common subproblems (sorting and matrix operations). Such algorithms are interesting not only on their own, but many problems from other areas of computer science can be reduced to them.

We analyze the algorithms in theory, by estimating their complexity – run time and space complexity as well as efficiency of their cache utilization. But asymptotic complexity hides many constants which might have a substantial effect on the real speed of the algorithm. We therefore benchmark the algorithms on real hardware in addition to the estimates. This helps us compare the algorithms to each other and also to determine how realistic the cache-oblivious model is.

Apart from previously known algorithms, we propose several new ones, most notably an algorithm for determining connected components in Section 9.2 and maximal matching in Section 10.3. We also examine few hybrid algorithms which combine cache-oblivious algorithms with classical ones. This helps, for example, to eliminate high overhead of recursive algorithms on small problems.

# 2. Conventions and used notation

There are many generally used notations when it comes to algorithms and bounds of their complexity. This is description of the one used in this text.

We use the well-known symbols  $\mathcal{O}$ ,  $\Theta$  and  $\Omega$  for denoting asymptotic estimates of functions. As these are, in fact, sets of functions (e.g.,  $\mathcal{O}(n)$  is set of all functions growing at most linearly in n), we use the set notation for relations between them. Therefore  $f \in \mathcal{O}(g)$  means that f grows at most as fast as g in asymptotic sense and  $\mathcal{O}(f) \subseteq \mathcal{O}(g)$  means that all functions growing at most as fast as f are growing at most as fast as g as well.

Generally, n denotes the number of elements or more generally, the size of the given problem.

# 2.1 Graphs

When we talk about graphs, we usually mean combinatorial graphs – some *vertices* (in other works sometimes called nodes) connected by *edges*. Unless explicitly mentioned, we work with undirected graphs – the edges have no direction. We implicitly assume that all graphs are finite and simple (there are no loops nor parallel edges).

Therefore, a graph is an ordered pair G = (V, E), where V is the set of the vertices and  $E \subseteq \binom{V}{2}$  are the edges (a subset of all unordered pairs of the vertices). When we estimate algorithm bounds and there's no room for confusion, we use V and E for sizes of the respective sets, too. That means, instead of writing  $\mathcal{O}(|V|)$  (functions growing at most linearly with the number of vertices), we write  $\mathcal{O}(V)$  (and similarly for edges).

# 2.2 Cache and memory

We assume a two-level memory hierarchy consisting of *external* and *internal* memory (there are often more levels than two in practice, but it would needlessly complicate matters). The internal memory is limited, while the external one is assumed to be infinite. The algorithm works directly with the data in internal memory and moves the data between internal and external memory. However, it is not possible to move the data in arbitrary way.

Both the internal and external memory are split into non-overlapping areas of a fixed size, called **pages**. It is possible to move the data by whole pages only – load a single page from anywhere in the external memory to any page of the internal memory. But if the page in the internal memory is not free (there are data in it), it must be freed first by storing the data to the page in the external memory where it was originally

taken from. This exchange of data in the page of internal memory is called *memory* transfer.

This terminology is taken from the I/O model (see Section 3.3). It suggests having a RAM as internal memory and a disk as external one. While the cache-oblivious model is applicable for such situation, it is more common to consider the CPU cache hierarchy. Therefore, sometimes, we interchange the terminology, we call the internal memory *cache*, the external memory just *memory* or *main memory* and the page is also called a *cache line*.

The size of the internal memory is denoted by M and the size of a single page is L. Therefore, there are M/L pages in the internal memory.

We assume the cache is **tall**, which means  $M/L \gg L$  – there are more cache lines than how the cache line is wide. This is realistic, as today processors have cache line sizes in order of tens of bytes (most common is 64B) and caches from tens of kilobytes to megabytes (depending on processor model and level of cache when multiple are present). This gives the number of lines in orders of thousands or more.

# 3. Computational models

Computer science uses asymptotic complexity to distinguish how good an algorithm is. The principles of asymptotic complexity are generally known and therefore we will not describe them here.

We usually estimate three properties of an algorithm we study. If not noted explicitly, the estimate is for the worst-case scenario.

**Time complexity** is the number of instructions executed during the runtime of the algorithm. This is the time measured in the RAM model (see Section 3.2).

**Space complexity** is number of memory cells needed to run the algorithm. We count the cells of external memory. We assume we use the whole internal memory, and we want to know how large the external memory needs to be (or how large size of the infinite external memory is used).

**Number of memory transfers** is just what it says – number of pages exchanged between the internal and external memory during the runtime of the algorithm.

When we evaluate space complexity, we have no serious problems, since it is generally agreed on we count the number of memory cells used during the computation. This can be easily formalised in a way in which it corresponds to the intuitive understanding.

The time complexity is more problematic, since there are multiple definitions of elementary operations (the instructions taking unit time). Since we will be comparing algorithms using multiple criteria, we use several models, each with slightly different elementary operations.

Note that all our models are Turing-complete (they have the same strength as a Turing machine), the models will differ only in how expensive an algorithm is in each one of them. We will also ignore questions regarding where the program is stored, if it is hardcoded in the machine (like in the case of a Turing machine) or stored in the same memory as data (Von Neumann architecture), since it would only complicate matters without providing any interesting differences.

When computing the complexity, we'll not do it in completely formal manner (listing each used instruction). We are interested in the asymptotic estimates only and we can afford little bit of intuition in the estimates. But we need to know what the estimates mean, therefore we list computational models interesting to the work.

## 3.1 Real hardware

This is not really a model, this is what we would like our programs to run fast on. We could measure it in processor ticks or other time units like seconds. However, we don't analyse the complexity for real hardware for several reasons:

The most obvious one is each computer is different. They have instructions that take different number of ticks on different processors (or completely different instructions), they have memories of different speeds and the speed of program is influenced by almost every other part of the computer.

The other reason is that even if we fixed one computer as given, it would be impossible to analyse. Even single instruction can take different times to run each time. One aspect of this is that processors run multiple instructions at once and they share the computation units inside. The operands might be in registers, or they might need to be loaded. If they are loaded, the time it takes depends on if it is stored in cache, on which level of cache hierarchy, or if the data come from main memory, if the main memory has the corresponding memory line addressed, or if other part of the computer blocks the bus. This complexity can be demonstrated for example by the Intel Architecture Optimization Reference Manual [2].

Therefore we either try to benchmark the implementations of algorithms, which is inaccurate and chooses only some finite set of infinite number of possible inputs (see Chapter 4). The other possibility is to use some simplified model, which gives some estimate of speed, but might ignore some aspects of the computer or turn out to be unrealistic in some of its aspects.

#### 3.2 RAM

RAM, or Random Access Machine, is the most commonly used model for estimating the time complexity and it is usually the abstraction used by procedural languages.

The computer in this model consists of a processor and a main memory. The main memory is infinite array of cells, each containing one integer number. The array is indexed also by integers. The processor executes instructions. Each instruction takes a fixed number of memory cells from the main memory, uses them as operands and stores the result back to the main memory. The location of each operand or result can be either a constant encoded in the program or indexed by a number stored in another memory cell. When indexing by an other cell, the position of this cell must be a constant encoded in the program (depth of indirection can be at most 1).

Each instruction takes unit time, which means that all memory locations are equivalent in their access time (and we completely ignore any of the irregularities of real hardware). This is not unrealistic, though, since a real computer has an upper bound of how long a single instruction takes.

There are several versions of this model differing in the allowed set of instructions. We'll try to stay close to real hardware, and we can say that the unit operations are exactly the primitive operations of the C language (which include arithmetics, logical operations, data copies and conditionals).

Some versions of this model include a finite number of registers inside the processor. It is easy to see that this makes no significant difference, since we can reserve a memory cell for each register and use it's index whenever we would like to use the register.

This model has some problems in being too strong. It is possible to compress the whole input into a constant number of memory cells and perform the whole computation on it, usually making it possible to finish the computation in constant time. Some versions of the RAM model try to solve it by limiting the maximal number which can be stored in single cell (which is close to real hardware, but limits the theoretical power to finite automata) or by charging time logarithmic in the size of the operands to the instruction. We'll simply avoid doing the compressions or any other kind of obviously unrealistic misuses of the model. The same problem applies to all of the following models.

# 3.3 I/O or Cache-aware

This model is inspired by a situation when the internal memory of computer is not sufficient and data must be stored in external memory (today usually magnetic discs or SSD devices).

We have a processor and internal memory, as in RAM. But the internal memory is finite and divided into pages. Each page contains a fixed number of continuous memory cells. To store the data, we have an infinite external memory.

The model allows using of all the instructions in RAM for free. But these instructions can work with the finite internal memory only. To access the external memory, we add two new instructions: **store** and **load**. These transfer a whole page of from internal memory to external memory or vice versa.

We count only the number of loads and stores. This corresponds to the fact that external memory is several orders of magnitude slower than the internal memory on real machines, therefore the whole computation time is dominated by the communication with external memory.

The model considers all external memory locations equivalent in their access time. This is seemingly not true for hard discs, since their seek times depend on the distance between previous access and the current one. But if we use pages large enough, the time to read or write the page (which is located consecutively on the medium) becomes comparatively long as the maximum seek time. This makes it possible to estimate the whole load and store by a constant time. Further justification of this can be found in [3].

The complexity in this model will be a function of the size of the internal memory and page size, as well as the properties of the program's input.

#### 3.4 Cache-oblivious

This is the model which will have most attention in this work. It was introduced in [1].

The model computer has the same parts as in the I/O model. However, the program running on it has no knowledge about the size of internal memory or the size of pages. The program sees only the infinite array of memory cells as in the RAM model (therefore we could say Cache-oblivious and RAM models have the same instruction set).

To make it possible, there's an abstraction layer. The internal memory is used only as a temporary cache. When the program accesses a memory location, the cell may be currently in the internal memory in which case it is simply used. If it isn't in the internal memory, the page containing it must be loaded from the external memory first. If there are no free pages in the internal memory, some page must be transferred to the external memory first (this is called eviction) to make room for it. The abstraction layer chooses optimally which page to evict (it is easy to see that the optimal page to evict is in fact the one which will be needed furthest in the future).

All this happens without the program knowing, while in the I/O model the program moves data explicitly. This is the reason to call the models Cache-aware and Cache-oblivious.

Similarly to the I/O model, we count only the number of pages transferred between internal and external memory. We analyse it relative to the properties of internal memory – while the program itself can't use the sizes, the analysis can.

We sometimes assume some minimal size of the internal memory, either in the number of memory cells or number of pages. In all cases, this will be constant, therefore we can still call the algorithm cache-oblivious (but with some kind of minimal requirements on the hardware it'll run on).

The use of the optimal paging strategy seems unrealistic. However simple LRU strategy (the least-recently used page is evicted) behaves asymptotically the same as the optimal one<sup>1</sup>. The optimal one is usually easier to analyse, especially when an upper bound suffices – we describe any strategy of how the pages are evicted and assume it's not better than the optimal one.

The motivation for this model comes from several areas. The obvious one is the same as with I/O model, when we have too much data to fit to the internal memory. But writing (or designing) programs for I/O is usually complicated, so we can provide a generic abstraction layer to take care of memory transfers and keep the core of the program simple. Something similar is done by many operating systems in the form of virtual memory (with the aid of hardware). If the computer runs out of internal

<sup>&</sup>lt;sup>1</sup>More precisely, the number of cache misses of LRU is within a constant factor of the optimal strategy with constant-factor smaller cache, as shown by [4].

memory, it stores some data on disk. This is usually called swapping (although this is only inexact an approximation of LRU).

The other motivation is modelling processor caches. Today processors have hierarchy of transparent caches for the data in the memory with various paging strategies (usually based on LRU, but some are enriched by heuristics to provide better performance in usual workloads). The caches are much faster than the memory. If we want to write programs that use the caches effectively, we would be interested in this model, since the caches differ from processor to processor (and from level to level in the hierarchy) and the cache can't be manipulated directly. Also, it can be shown that if an algorithm behaves optimally in a single-level cache hierarchy, it behaves optimally in a multi-level cache hierarchy as well, as proven in [1].

# 3.5 Streaming model

The reason for its existence is the same as with the I/O model, but comes from the time when computers used magnetic tapes as their external memory. Considering all positions on a tape as equally fast to access is clearly unrealistic.

In this model, we have a finite internal memory and a finite number of streams. Each stream is a possibly infinite sequence of integers. We can read or write data at the current position in stream. Furthermore, we can move one position to the left or right in the stream. It is enough to count the number of moves between positions (we can cache the current cell if we would be reading or writing it multiple times between the moves).

As this model is very limited compared to what today computer can provide, algorithms are no longer directly designed for it. But if an algorithm happens to be fast in this model, it can mean it will perform well on real hardware. Hard disks are faster if data are read and written sequentially. The same holds for memory systems (sequential access is good for both cache evict and prefetch heuristics and for memory modules with matrix indexing – this is explained by Ulrich Drepper [5]).

#### 3.6 Parallel modifications

This is not a model of itself. It is more a modification to other models. The computer has multiple processors. In the PRAM model (parallel extension of the RAM model), they have one main memory each and another main memory shared between all of them (which can be used for communication). In the other models, each processor has its own internal memory and the external memory is shared.

We assume it is possible for multiple processors to read the same memory location at the same time, but they never write to the same location (or page, we assume they have some kind of synchronization to accomplish this) at once. This is known as CREW (Concurrent Read Exclusive Write). Usually only the RAM model is considered in the parallel form called PRAM, but it is possible to extend it naturally to other models.

We can either sum the number of transfers/operations of all processors or take the maximum of them, assuming the one will take the longest to run, therefore the real runtime will depend on it (or, taking the critical path, if they wait for each other). But we'll not generally compute the complexity for parallel models, only note that a given algorithm can be written so it benefits from the parallelism.

The motivation here is to model multi-processor and multi-core computers.

# 4. Benchmarks

In addition to asymptotic analysis of complexity of our algorithms, we have implemented them and measured their performance on real hardware. To do so, a benchmark framework was created. To understand what was actually measured, here's a description of the framework.

Some of the results are used through the text. More are included in Appendix A. The code is available on the attached CD or online at http://vorner.ucw.cz/en/thesis/.

# 4.1 Pointers and benchmark types

There are several things to measure, each requiring different instrumentation inside the running algorithm. Including all would slow the algorithm down in cases it is not needed, skewing the results. Writing several versions of each algorithm would be repetitive and it would be possible for the versions to differ.

Therefore the algorithms are implemented as C++ templates which allow replacing classes used as pointers. The pointer class actually used performs the needed instrumentation. This allows building a binary with the correct instrumentation just by specifying the corresponding pointer class.

## 4.1.1 Measuring runtime

To measure runtime of the whole algorithm, we need no instrumentation – it would actually seriously skew the results. Therefore the pointer class used is just a thin wrapper around the real pointer. The compiler optimises all the calls out, changing it to the primitive CPU instructions, which produces code equivalent or close to an algorithm written in the usual way, with real pointers (or arrays).

It is then possible to simply run the algorithm and compute the runtime by comparing the time before starting it and after it finishes. Sometimes the same test case was run multiple times to minimise random effects of operation system and time measurement inaccuracies. In such case, the total time is reported in the graphs.

It is also possible to run multithreaded. This is not possible with the other benchmark types, mostly because of some low-level technical issues which were not attempted to be solved.

The benchmarks were run on AMD Phenom II CPU at 3.3GHz with 6MB of L3 cache and 6 cores. There were 4 memory banks at 1300MHz frequency. The used compiler was gcc 4.5 with optimisation flags -03 -march-native. It was run on Linux 3.2.

#### 4.1.2 Measuring LRU cache of disk

The goal here is to simulate the case where internal memory is a cache for data stored on a disk. There are two things needed to make the cache work, as suggested in Section 3.4.

The first one is knowing when and what page needs to be loaded. Having a check in each access to a pointer would be needlessly slow. But when the memory is allocated by mmap system call, only the address space is reserved. The physical pages of memory are assigned only when first accessed<sup>1</sup>.

Now, we can use mprotect to make the address space we reserved inaccessible. Whenever the algorithm tries to access such inaccessible page, a segmentation fault signal is generated. If we register a handler for the signal, we can use it to make the page accessible again and load data into it from disk (using direct I/O, to make sure the data aren't kept in some OS cache, which would make the results useless). When evicting a page, we munmap it (so the physical page is freed), then mmap and mprotect the page again, so we can check when it should be loaded.

The other needed thing is to know which page should be evicted. We inject code to all operations with pointers. Whenever data is accessed through a pointer, the access is stored in an auxiliary buffer. The data in buffer is used to compute the page for eviction.

This allows for specifying both the size of the cache and the page (provided it is multiple of the hardware page size) and makes measuring the time the algorithm needs to run when data are loaded and stored on disk. However, the algorithm runs slightly slower, because of the writing to buffer and computation of LRU. It is assumed that this slowdown will be less significant than the time needed for actually storing and loading data.

However, this method has a problem. The data are stored on unpredictable place on the disk, so the results can differ between runs of the benchmark. Empirical observation suggests that this difference is not significant, but the results shouldn't be taken too strictly.

# 4.1.3 Simulating cache behaviour

This is more theoretical measurement than the previous ones. The goal is to count how many cache misses would happen on a provided cache, if the cache was at the sole use of the algorithm.

To do this, the pointers are modified to output address and length of each access. These

<sup>&</sup>lt;sup>1</sup>While it doesn't seem to be guaranteed by the POSIX standard, it was experimentally confirmed to be the case on the used Linux system.

addresses and lengths are output through a pipe. A different program reads the data and simulates behaviour of caches with given properties, simply by keeping the list of pages in the cache and information about accesses so it can decide what pages should be evicted. By simulating multiple caches of different sizes or with lines of different lengths we can study both how an algorithm reacts to changes of input size as well as changes to the cache properties.

This is not completely accurate. This doesn't take the local variables in functions into account. But we can assume they would never be evicted from the cache, so the only inaccuracy is they don't take space in the cache, which is negligible. For this to be true, we unroll all recursion and use an explicit stack. This way, there's only a constant number of local variables (or global ones) and everything else is allocated on the heap and accessed through the instrumented pointers.

# 4.2 Inputs

The algorithms need to be tested on some inputs and the type of an input can influence the results quite substantially. Therefore the inputs are described here.

#### 4.2.1 Sorting inputs

There are three kinds of inputs we have used for benchmarking of the sorting algorithms (in Chapter 6):

- All zeroes. This input is used to make sure that the algorithm works on unusual input.

- Random input. Each value in the input is generated randomly with uniform distribution. This is the method used for graphs and results through the text, but the Apendix A.1 contains other inputs as well.

- Already sorted input. This input checks if the algorithm takes any benefit from the sorted state.

Also, various data types are used (the results differ slightly depending on the size of a single item).

# 4.2.2 Matrix inputs

The matrix multiplication (in Chapter 7) is measured using random inputs – cells of each of the input matrices are filled by independent random integer with uniform distribution.

#### 4.2.3 Graph inputs

All the inputs for graph algorithms (in Chapters 8, 9 and 10) are graphs with at least a little bit of randomness. However, it is slightly problematic to say what a random graph is. They are listed with the names as they appear in the text (note that this is not the definition of graph property, just a name of the input type).

- **Dense** graph here is one where each possible edge is present with a fixed probability, independently of other edges. The probability used in the benchmarks is 1/10, therefore the expected number of edges is  $\frac{|V|\cdot(|V|-1)}{20}$ .

- **Sparse** graph is a graph generated by adding edges until it has  $c \cdot |V|$  edges (or if the graph has too few vertices, all possible edges). The edge is chosen by taking two random vertices independently with uniform probability. The edge is discarded if it is already present or if it is a loop. The constant c is 10 unless explicitly stated differently.

- **Tree-like** graph is like the above, but with c = 1.

- A *triangulation* is generated in this way: We start with a triangle. The triangle divides the plane into two faces. We pick one of the existing triangular faces, put a new vertex into it and connect to all three vertices on the border of the face. This breaks the face into three new ones. We again pick a triangular face (not necessarily one of the new ones, but one that was not yet broken) and repeat, until we have enough vertices. Each edge is preserved with probability of  $\frac{9}{10}$ .

All the generated graphs are simple – they have no loops and no parallel edges. The triangulation one is guaranteed to be planar. Planar or mostly planar graphs are common in practice, they can represent networks, maps and similar (which are often large), so we are interested in how the algorithms perform on them. The treelike and dense graphs are used as extremes in the ratio between edge and vertex numbers.

# 5. Common techniques

We are going to describe or design several algorithms in the following chapters. Therefore we need to known some common techniques and tricks of designing and analysing them.

# 5.1 Algorithm approaches

Let us first look at how the cache-oblivious algorithms are usually built. That means there can be other techniques or tricks in some algorithms, but these are quite common.

#### 5.1.1 Scans

The most basic design approach is to have data in an array and access elements sequentially, from left to right or in the other direction. It often happens we need to access all the elements, for example if we want to compute the sum of all of them. In such case, this approach is optimal. We need to access each page of the array at least once, as we need to access an element in each of the pages. This means we have  $\Omega(n/L)$  memory transfers in case the array is not present in cache. And the scanning algorithm does  $\mathcal{O}(n/L)$  transfers, as each page of the array is processed as a whole and never touched again when a different page is accessed. We can keep this "active" page in the internal memory.

As the scan needs only a single page, there can be a constant number of scans running in parallel (meaning that one array is not scanned at once, but part of it is scanned, then part of another array, then continuing the first one, and so on).

Scanning a constant number of arrays in parallel is also a common technique, and, while simple, it is quite powerful.

One example would be merging two sorted arrays to one. We look at the beginnings of the arrays and compare them. The smaller one is output and we move forward in that array. We again compare the values in the arrays and repeat until we run out of the inputs. As we move only forward both in the input and output arrays, this is equivalent to scanning the three arrays in parallel.

Another example would be finding out what values are present both of two sorted arrays. If the beginnings of the arrays are equal, we found a value which is in both. If not, we skip the smaller one, because we know it is not present in the other array, due to it being sorted. Then we try to compare them again.

Scanning arrays  $A_1, \ldots, A_n$  in parallel if n is a constant clearly takes  $\mathcal{O}\left(\frac{\sum_{i=1}^n A_i}{L}\right)$  memory transfers.

**Note:** We often need to access the elements in some specific order. Therefore many algorithms combine sorts and scans.

**Note:** Scan is also optimal in the streaming model. Algorithms using only scans and sorts are expected to perform well in the model. There are algorithms designed for the streaming model. We can find some sorting algorithms for the streaming model for example in The Art of Computer Programming, Volume 3 [6], Chapter 5.4.

#### 5.1.2 Divide and conquer

Divide and conquer is a well-known programming technique. It means taking the problem, and by applying some relatively primitive transformation turning it into few smaller problems. The smaller problems are then solved recursively and their results are aggregated to form the result. The recursion stops when the problem turns small or simple enough to solve it trivially.

The advantages for the cache-oblivious model are twofold. First, it is usually possible to design the splitting to smaller tasks and aggregation in a cache-oblivious friendly way, using only sorts and scans. Secondly, sometimes it is possible to prove that the bottom levels of recursion will be free of memory transfers. Since the tasks are getting smaller and smaller, they'd become smaller that the whole cache.

### 5.1.3 Dividing vertices to conquer edges

This is the Divide and conquer approach applied in a less traditional way. The goal is to split edges in small enough groups so they can be handled (the vertices are not important for many algorithms, they simply "pin the ends of edges to the surface so they don't curl up").

We assume the vertices are identified by integer numbers  $0, \ldots, |V|-1$  and the vertices are pairs containing both their endpoint vertex indices.

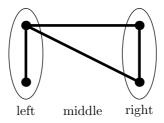

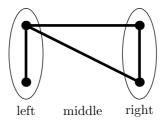

But instead of taking the array of edges and dividing it into two halves, we take the vertices and form two groups of them. We will call them *left* and *right*. This will create three groups of edges. The *left* and *right* group of edges have both endpoints in the left or right group of vertices respectively. The edges in the *middle* group connect vertices of both groups, so each edge has one left and one right endpoint.

But there's a problem. When we get deeper in the recursion, the vertex groups get smaller and smaller. However, if we look at the graph defined by the middle edge group, we see that the graph potentially contains all the vertices. With a bad choice of how to split the vertices – for example taking the halves with smaller indices and bigger indices, the middle group could stay the same size across any number of levels of recursion. We need a rule how to split the vertices to make sure the number of edges in each group is bounded.

Figure 5.1: Vertex and edge groups

We choose following rule to split the vertices. If we are i levels deep in the recursion, we look at the value of the i<sup>th</sup> bit of each vertex. The value of the bit decides which group the vertex goes to.

As there are  $\log_2 |V|$  bits in the vertex indices, the recursion must after so many levels. This does not give groups of edges of size at most 1, but it provides groups with special properties we can use, as shown bellow in Lemma 2.

**Note:** We don't need the vertices explicitly, the splitting of edges can be done by scanning through them and just looking at their endpoint numbers.

#### 5.1.4 Van Emde-Boas layout

We want to store a complete binary tree (the tree doesn't have holes and all the branches are of the same length) in memory. We want to traverse it from root to one of the leaves. But the usual approach with pointers is not very cache friendly, so we show a different layout.

We notice that storing data in an array is usually good for caches. The first idea for a layout in an array would be to place it by layers. First, the root is stored. Then the two sons, then the four nodes in depth 2, etc – similar to how an ordinary binary heap is usually stored. However, from some point the levels become longer than a page, so the sons are in a different page than the parent. The best thing we could do would be storing the top of the tree in the cache, but this would still be  $\Theta$  (max 0, log  $n - \log M$ ) memory transfers.

Therefore we need a more sophisticated layout. The idea is inspired by the van Emde-Boas tree [7], however, the data structure is different. It can be found for example in Cache-oblivious B-trees [8].

Assume we have a complete binary tree. It would work for different trees as well, but it would be harder to explain. We also ignore rounding for simplicity. There are two reasons why we can do it. One of them is this is a general design approach, not a concrete data structure. Another is it is not important<sup>1</sup>.

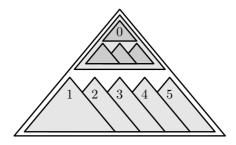

The tree has approximately  $\log_2 n$  layers. We cut the tree in the depth of  $\frac{\log n}{2}$  into an upper and lower part. The upper part has  $\Theta(\sqrt{n})$  leaves and the bottom part is composed of  $\Theta(\sqrt{n})$  trees. All these trees are of approximately the same size.

We store the top tree, followed by the bottom trees into the array. Each of these trees is laid out in the same manner recursively. The layout is illustrated in the Figure 5.2.

Figure 5.2: The recursive layout (numbers mean order in the array)

The advantage is, as we are splitting the trees into smaller and smaller ones, we eventually get to trees small enough to fit whole in a constant number of pages. This constant number of pages fit into the internal memory, therefore we need to load each of them at most once when finding our path through such a tree. That means we can go from top to bottom of the tree with  $\mathcal{O}(1)$  memory transfers.

But the tree has  $\Theta(L)$  nodes, therefore it is  $\Theta(\log L)$  levels deep. We pay  $\mathcal{O}(1)$  memory transfers for each  $\Theta(\log L)$  layers. The total cost of traversal of the whole large tree is therefore  $\Theta\left(\frac{\log n}{\log L}\right)$ .

### 5.2 Common lemmata

There are several lemmata used through more than one chapter, so they are listed here. A function f satisfying  $f(n_1) + f(n_2) \ge f(n_1 + n_2)$  is said to be **sub-additive**.

**Lemma 1** (Number of memory accesses of a recursive algorithm). We have a recursive algorithm which splits a task into a constant-bounded number of subtasks of total size no bigger than the original size. The input is of size n. The depth of recursion is  $\mathcal{O}(g(n))$

<sup>&</sup>lt;sup>1</sup>As mentioned in the original article [8], correct rounding is important for dynamic data structures, but we use the layout in static data structures only.

for some non-decreasing function g and the cost of local work of a task of size m is  $\mathcal{O}(f(m))$ , where f is a sub-additive function. Then the algorithm needs  $\mathcal{O}(g(n) \cdot f(n))$  memory accesses.

*Proof.* We would like to take a sum of costs of all the tasks on a single level and multiply it by the number of levels. This would be possible for the sub-additive function f.

The problem is, the f(n) could be smaller than 1 for small enough n. But a task of such size would still require a full memory transfer. Example of this could be scanning an array. The cost is  $\mathcal{O}(n/L)$ , but if n < L, a whole page (or two, in fact, if the data are placed on the border of pages) would need to be loaded. These memory transfers are "hidden" in the  $\mathcal{O}$  notation and are not really interesting most of the time. However, summing the cost over many such small tasks would not be correct unless we can prove the needed part of the page would be already present in the cache.

We fix a small constant c. We'll define three kinds of tasks:

- A *large* task is such a task of size m, where  $f(m) \ge c$ . Therefore the cost of the task itself is large enough to amortize the costs of partial pages.

- Then we'll have a *small* task. This is a task whose computation (including subtasks) fits into the internal memory. Therefore if the whole input was read into it before, it would cost no memory transfers. Or, if we look at it differently, the only cost paid for this task is to read the input in.

- Last, a *tiny* task is one where the parent of the task is small. The tiny task is for free, since it is by definition small and it is already read into the internal memory by the parent.

There's no problem with large tasks, nor with tiny. There's at most one task which is small but not tiny on each path from the root of the recursion tree to a leaf. We claim that this small task has a large parent and we'll amortize the constant number of transfers to the parent (we can, since each large parent has a constant-bounded number of children).

If there wasn't a large parent, there would have to be a task that is neither small nor large. Such task would not fit into the cache completely. Therefore f(m) > M/L, as it isn't small. But f(m) < c, as it is not large.

However, as we noted already, we assume that the cache is tall. That means specially that it has more than constant number of cache lines, therefore a task that does not fit must need more than constant number of transfers. Therefore a task must be either large or small.  $\Box$

**Lemma 2** (Dividing vertices). If we have a recursive algorithm dividing the vertices to conquer edges (from Section 5.1.3), no two edges in the same task on the bottom level of recursion share a common vertex.

*Proof.* We'll prove this by a contradiction. Assume that there are two edges,  $e_1, e_2$  that share a common vertex v. Since the graph is simple, there are no parallel edges and the other ends of the edges must be distinct, let us call them u and w.

On each level of the recursion, we examined one of the bits in the IDs of vertices. Furthermore, on each level, both edges ended up in the same group – otherwise they would not be in the same task at the bottom of recursion.

We'll denote the  $i^{th}$  bit of the ID of the vertex x as x[i].

We look at a single level i, therefore examining the  $i^{th}$  bit. If both the edges ended in ether left or right group, the u[i] = v[i] and w[i] = v[i]. This means u[i] = w[i].

If they ended in the middle group,  $u[i] \neq v[i]$  and  $w[i] \neq v[i]$ . However, the value of a bit can only be 0 or 1, therefore u[i] = w[i].

As the edges always ended up in the same group, the u and w are equal in all their bits, therefore u = w. This is contradiction.

# 6. Sorting

This work concentrates mostly on graph algorithms. However, as shown below, many of the algorithms use sorting as their subroutine and this sorting influences their bounds. Therefore we analyze sorting algorithms first, including the number of memory transfers.

First of all, we analyze several well-known sorting algorithms, then we show an algorithm designed for the cache-oblivious model.

# 6.1 Merge sort

Assume for a while the input array is of size  $n = 2^i$ . It'll simplify the description and we'll show how to get rid of it later.

This algorithm first divides the input into n blocks each of them consisting of a single element, so all of them are trivially sorted. Then, in each iteration, it takes two sorted blocks of the same size and merges them together. The way the blocks are chosen is described below, as there are multiple possibilities.

Merging them means we look at the first element of each block. We takes the smaller one, output it and advance in the respective block to the next element. We then repeat this action until we get to the end of one of the blocks. Then we append the rest of the other one to the result. We can notice the result will be also sorted.

When we have only one block, the array is sorted.

If we want to sort an array of a different size than  $2^i$ , we can do a trick. We extend the array with virtual elements which are larger than anything, so the input has the correct size. This will make it at most twice larger, therefore it won't hurt the complexities. After sorting, we can remove these elements from the end of the array.

Furthermore, we notice these would always be at the end of a block. Therefore we don't need to store them, we simply have some smaller blocks and pretend the blocks are of the full size – this only means less work and used memory.

However, we still use the assumption in the analysis.

**Theorem 1.** The algorithm runs in  $\mathcal{O}(n \cdot \log n)$  RAM time.

*Proof.* When we merge two blocks to create a block of size s, it clearly takes  $\mathcal{O}(s)$  time. This is  $\mathcal{O}(1)$  per an element. Whenever an element takes part in a merge, it gets into twice as large block, because the other block is of the same size. Therefore an element can participate in  $\mathcal{O}(\log n)$  merges. So the total is  $\mathcal{O}(n \cdot \log n)$ .

**Theorem 2.** The algorithm needs  $\mathcal{O}(n)$  memory.

*Proof.* A merge can be done with linear amount of additional memory. And we can discard the smaller blocks once we merged them (or reuse the memory).  $\Box$

**Theorem 3.** The algorithm would require  $\mathcal{O}\left(\frac{n}{L} \cdot \log n\right)$  memory transfers, if there were no partial pages at the beginning or end of the blocks.

*Proof.* This is very similar to the proof of theorem 1. We need to notice that a merge can be done in  $\mathcal{O}\left(\frac{n}{L}\right)$  memory transfers, as we read the inputs sequentially and write the output sequentially (so we can have a memory page for each of them, holding the active area).

There are two common ways in which the merge sort is implemented. We look at a merging tree. Each node is a block which existed during the runtime of the algorithm. Sons of block b are the blocks used as inputs to create b.

#### 6.1.1 Layered

First, all the blocks of size 1 are merged together to form blocks of size 2. Then, all these are merged to form blocks of size 4, and so on. We go from bottom up in the merging tree.

The merges on a single layer are performed from the left to the right. We can use a queue for the blocks, each time taking two blocks to merge from the beginning and putting the result to the end of it.

**Theorem 4.** The layered version of merge sort requires  $\mathcal{O}\left(\frac{n}{L} \cdot \log n\right)$  memory transfers.

*Proof.* We can imagine that the whole input is scanned two times in parallel and the whole new level is written sequentially as the output. Therefore the merging on a single layer takes  $\mathcal{O}\left(\frac{n}{L}\right)$  memory transfers – there can be only one partial page at the beginning and one at the end of the level.

The queue operations take  $\mathcal{O}\left(\frac{q}{L}\right)$  memory transfers for q operations (as we can have a page for the beginning and a page for the end of the queue, effectively having a writing scan and a reading scan). There are  $\mathcal{O}\left(n\right)$  operations with the queue, therefore this part of the cost is smaller.

Therefore we can use the theorem 3 and get the result.

#### 6.1.2 Recursive

If we consider the merge tree again, this version goes through it in a DFS order. We call the algorithm on the whole array to obtain the final result. That call would like to

merge the two halves of the array together, but they must be sorted first. So it calls the algorithm recursively on the left and right half. Once they return, the final result is obtained by merging their results.

**Theorem 5.** The recursive version of merge sort takes  $\mathcal{O}\left(\frac{n}{L} \cdot \max\left(1, \log n - \log M\right)\right)$  memory transfers.

*Proof.* To merge two blocks, we need  $\mathcal{O}\left(\frac{s}{L}\right)$  memory transfers if the size of the result is s. This function is sub-additive and the size of the levels is the same through the recursion. There are two children of a task. There are  $\log n$  levels of recursion, but the tasks of bottom  $\log M$  levels fit into the memory completely, so we can simply count  $\log n - \log M$  levels of recursion. We can use the Lemma 1 and get this result.

We need to at least read the input in if n < M at least, which costs n/L – there are enough pages for the whole input, so the order in which we access them does not matter.

# 6.2 Quicksort

Another sorting algorithm commonly used on the RAM is Quicksort [9].

While this algorithm doesn't guarantee the optimal RAM bounds in the worst case scenario, it achieves them in the expected case. It is not true in the cache oblivious model. However, as practice shows, it is very fast on real hardware.

The algorithm is defined in recursive way as follows:

- 1. If the input array is at most 1 element large, it is trivially sorted, so it is returned.

- 2. Otherwise, an element from the array is selected. We call this element a *pivot*.

- 3. The array is split into two parts containing smaller and larger elements than pivot respectively.

- 4. Each part is sorted recursively.

- 5. The smaller part, pivot and larger part are concatenated together and returned.

**Note:** In case the input array may contain duplicate elements, it could happen there are elements equal to the pivot. In such case, we can put these elements in either part or create a third part of elements equal to pivot. The third part would not be sorted recursively.

The usual implementation splits in following way. It scans the input array from both ends in parallel. We first find an element larger than the pivot on the left side. Then we find an element smaller than the pivot on the right side. These two elements are

then swapped. This is repeated until the scanning positions meet somewhere in the middle. The place where they meet is the boundary between parts, as now the left side contains only elements smaller than the pivot and the right side the larger ones. Some care must be taken to make sure the pivot ends up in the middle in between and is not included in either of the parts. The position of pivot can, of course, change.

This implementation has three advantages: First, we don't need an auxiliary array, all the data are kept inside the input one. Second, the splitting is done by a scan, which is cache friendly. And third, the concatenation step is not needed, as the parts are already concatenated in the right order.

**Theorem 6.** The algorithm can be implemented in a way it needs  $\mathcal{O}(\log n)$  additional memory.

*Proof.* All data are kept inside the original array. The only additional memory needed is for the stack for the recursion. Every time we split the array, we can put the task with more elements onto the stack and start working on the smaller part immediately. This ensures that each time we put something onto the stack, the size of current task drops at last twice and it can grow again only when taking something out of the stack.  $\Box$

**Lemma 3.** An element participates in O(n) splits.

*Proof.* As the pivot is not included in either of the parts, the total size drops at last by 1 on each level. Therefore we run out of elements after n splits.

**Lemma 4.** It takes  $\Theta(n)$  time to split array of n elements.

*Proof.* In each constant-time step, we move the left position one step to right or the right position one step to left. This makes the positions one element closer to each other. They were at distance n-1 at the beginning so after so many steps they meet.

**Theorem 7.** The worst-case RAM time complexity is  $\mathcal{O}(n^2)$ .

*Proof.* Directly follows from Lemmata 3 and 4, as each level of recursion contains at most n elements.

**Lemma 5.** It takes  $\mathcal{O}(n/L)$  transfers to split array of n elements.

*Proof.* The splitting is equivalent to scanning the array in parallel from left and right at the same time. It is enough to keep one active page on the left side and one active on the right – each page will be transferred into the cache at most once.  $\Box$

**Theorem 8.** The algorithm needs  $\mathcal{O}(n^2/L)$  memory transfers in the worst case.

*Proof.* We simply combine Lemmata 1, 3 and 5. The size of levels is decreasing, the n/L function is sub-additive, there are 2 children to a task and there are  $\mathcal{O}(n)$  levels.  $\square$

**Theorem 9.** Quicksort runs in  $\mathcal{O}(n \cdot \log n)$  time on average.

The proof of this well-known fact is somewhat technical and not interesting for the purpose of this work. Therefore we omit it here. A complete analysis including average number of comparisons was presented by Ian Parberry [10].

**Theorem 10.** Quicksort requires  $\mathcal{O}\left(\frac{n}{L} \cdot \log n\right)$  memory transfers on average.

*Proof.* We would like to use Lemma 1 to compute the cost. However, we don't know the correct average recursion depth.

But we can notice the proof of the Lemma uses the recursion depth to compute the total cost of tasks over all the recursion levels only. Fortunately, we can compute the total cost differently. We notice the RAM run time of task sized m is  $\Theta(m)$ . The whole  $\mathcal{O}(n \cdot \log n)$  run time from Theorem 10 is composed only from these tasks. The task sized m needs  $\mathcal{O}(m/L)$  memory transfers, as shown in Lemma 5. Therefore the sum of all tasks will be also L times smaller than the RAM time bound, which is  $\mathcal{O}\left(\frac{n}{L} \cdot \log n\right)$ .

We notice the rest of the proof of Lemma 1 can be applied as the Quicksort algorithm satisfies all the assumptions.  $\Box$

### 6.3 Funnel sort

The Funnel sort algorithm is designed directly for cache-oblivious model. It was introduced by H. Prokop [1]. It was later made lazy by Brodal and Fagerberg [11], which makes it slightly simpler to implement.

It is inspired by merge sort, but instead of merging two streams in one step, it uses a device called funnel to merge more than two inputs at once. Overall, it splits the input into  $\sqrt[3]{n}$  parts of equal size, sorts each of them recursively, then it builds a funnel on these  $\sqrt[3]{n}$  inputs to merge them into output. To solve the small cases where 8, we can sort the input in some other way.

We will ignore rounding errors in the rest of the explanation, as they are not interesting.

#### **6.3.1** Funnel

The crucial part in the algorithm is how the funnel looks like. The purpose is to build a device that merges all its inputs together. If there are k inputs, we'll call it a k-funnel.

The funnel is a tree of mergers – places where two streams are merged together. The mergers are connected by intermediate buffers.

The tree and the buffers are laid out in the van Emde-Boas way (see Section 5.1.4). Therefore a k funnel is composed of  $\sqrt{k} + 1$   $\sqrt{k}$ -funnels. One is at the top and the

outputs of the rest are connected through the buffers to the inputs of the top one. These  $\sqrt{k}$ -funnels are build of  $\sqrt[4]{k}$ -funnels, etc. An illustration can be seen in Figure 6.1.

Figure 6.1: k-Funnel consisting of  $\sqrt{k}$ -funnels

Each funnel is connected to buffers. They are either the buffers containing inputs and a buffer to hold the whole output in case of the biggest funnel, or some intermediate buffers in case of the smaller funnels. The intermediate buffers always connect two k-funnels together. Such buffers are  $k^3$  elements large. This goes in the way of the van Emde-Boas layout, as smaller funnels contain smaller buffers.

This looks like a merge sort, we have a tree of mergers to merge longer and longer streams together to form the final one. However, there are differences. The first one is, the tree in the merge sort was implicit, but it is build explicitly in the form of a funnel here. The other one is the merge sort merges the whole inputs at once before moving to a different streams. We'll be switching between the mergers during the work of a funnel.

Each time a funnel is invoked, it tries to fill its output buffer. This is delegated to the top sub-funnel A recursively, as that one shares the output buffer. The funnel A either finishes because the output buffer is full, in which case we are done. The other possibility is it runs out of data in one of its inputs. The funnel A suspends the work and the funnel B below the buffer is invoked to fill it up. After B finishes, the work of A is resumed.

If the input buffer can not be refilled, because it is the input buffer and there's no funnel below it, or because the funnel below it already run out of all its inputs, the input is no longer used.

#### 6.3.2 Estimates

**Theorem 11.** The funnel sort takes  $\mathcal{O}(n \cdot \log n)$  RAM run time.

*Proof.* For this proof, we will assume that all the mergers exist for the whole life of

the algorithm. This is not true, as they are created and destroyed during the recursive calls of the algorithm, but it won't change the run time needed to create them all beforehand and destroy them all after the algorithm finishes.

We look at the complete tree of mergers, connected together from all the funnels. The top-level merger processes n elements. The ones directly below this merger process n/2 elements each. Generally, a merger processes half the number of elements processed by the merger above it. This means there are  $\mathcal{O}(\log n)$  mergers on the path of each element. As processing a single element in a merger takes constant time, this is  $\mathcal{O}(n \cdot \log n)$  over all the elements.

We also need to look at the work needed to construct the funnels. We notice the funnels correspond one-to-one with mergers, as each funnel has a merger at its very top. The tree of mergers have n leaves, therefore it contains  $\mathcal{O}(n)$  mergers. Building a funnel costs a constant time, including the buffer. This is smaller than the actual merging.

#### **Lemma 6.** A k-funnel takes $\Theta(k^2)$ memory.

*Proof.* There are some mergers and buffers in the funnel. As each merger has a buffer of at last one element (except the topmost one), we can count only the size of buffers, the sizes of mergers will amortize in this.

There are  $\sqrt{k}$  buffers of  $k^{\frac{3}{2}}$  elements, together taking  $k^2$  elements. Additionally, we need to count the buffers of the  $\sqrt{k} + 1$  smaller funnels. Therefore we would need to solve this recurrence:

$$S_k = \left(1 + \sqrt{k}\right) \cdot S_{\sqrt{k}} + k^2. \tag{6.1}$$

If we look down to the smallest funnels (e.g., 2-funnels), there are  $\mathcal{O}(k)$  of these (as there are clearly  $\mathcal{O}(k)$  mergers total), each having a buffer of  $\mathcal{O}(1)$  size. The leaves therefore take  $\mathcal{O}(k)$  memory, while the root of recursion takes  $\Theta(k^2)$ . Therefore the root size dominates and the total memory consumed by k-funnel is  $\Theta(k^2)$ .

#### **Theorem 12.** The algorithm needs $\mathcal{O}(n)$ additional memory.

*Proof.* We need an additional memory for three purposes. One of them is the stack for the recursion and traversing the active funnel. It is easy to see that  $\mathcal{O}(\log n)$  stack is enough.

The other reason is, when we are merging by a funnel, we need to preserve the inputs while already writing the output. But if we allocate a temporary buffer of corresponding size for each level of recursion, we are safely within  $\mathcal{O}(n)$ , as the size of input decreases exponentially within the recursion.

The last kind of memory is the one occupied by the funnels. But we notice there's only one funnel constructed at each time and the biggest one in existence will be the top-level one with  $k = \sqrt[3]{n}$  inputs. Therefore it takes  $\Theta\left(n^{\frac{2}{3}}\right)$  memory.

**Theorem 13.** The algorithm needs  $\mathcal{O}(\frac{n}{L} \cdot \log_{\frac{M}{L}} \frac{n}{L})$  memory transfers. This is optimal.

First, let us have a look at it intuitively. With merge-sort, we got the lowest levels for free, because the subtasks fit entirely into the cache. Now, we get some free levels in each depth of the recursion, as there are small funnels everywhere. We pay only when we're working with large funnels, but these are built of small funnels as well.

*Proof.* As shown by Aggarwal and Vitter [3], the lower bound for permuting n elements in the I/O model is the amount stated here. As sorting performs a permutation, it must cause at least as many memory transfers. It is easy to see that a lower bound for the I/O model is also a lower bound for a cache-oblivious model. Therefore when we prove the upper bound, we know it is the best possible result we can get.

The rest of the proof is inspired by the one written by Demaine [12].

First, we'll reformulate the tall cache assumption to  $M \geq L^2$  for the rest of the proof.

**Lemma 7.** A k-funnel causes  $\mathcal{O}\left(\frac{n}{L} \cdot \log_{M/L} \frac{n}{L} + k\right)$  memory transfers during processing of n elements, provided  $n \geq k^3$ .

Proof. Consider the biggest l such that the l-funnel fits into M/4 memory. As the funnel takes  $\Theta(l^2)$  space, the  $l < \frac{\sqrt{M}}{2}$ . And because of the tall cache assumption, there are at least  $\sqrt{M}$  pages in the internal memory, therefore we have enough free pages to keep a page for each of the l input buffers and another page for the output. This means that merging by this funnel is equivalent to scanning the inputs in parallel in the number of cache misses. This is m/L for m elements.

To load the entire l-funnel into internal memory, we pay  $\mathcal{O}(l^2/L + l)$  transfers. As the funnel is the biggest fitting,  $l \in \Omega(\sqrt[4]{M}) \subseteq \Omega(\sqrt{L})$ . From this, we conclude that  $\mathcal{O}(l^2/L + l) \subseteq \mathcal{O}(l^3/L)$ . Therefore, if  $m \geq l^3$ , the cost of reading the funnel in is amortized in the cost of merging the elements.

This is in the case the input buffers of the l-funnel contain enough elements. If we run out of an input buffer, we invoke the funnel below it. When we return to the current l-funnel, we might need to read it in again. However, as the input buffer below is at least  $l^3$  elements large, we can amortize the cost of reading the funnel in from those. This means, each block of at least  $l^3$  elements pays for three things. Loading the l-funnel below the buffer when we start producing the block, loading the l-funnel above the buffer after we finished the block and the actual processing of the elements.

This means the amortized cost of moving one element through one l-funnel is  $\mathcal{O}(1/L)$ .

Because  $l \in \Omega(\sqrt[4]{M})$ , there are  $\mathcal{O}\left(1 + \frac{\log k}{\log M}\right) \subseteq \mathcal{O}(1 + \log_M k)$  l-funnels on the path of an element. So, to merge n elements, we would pay  $\mathcal{O}(\frac{n}{L} \cdot \log_M k)$ .

We also need to pay a full memory transfer for each of the k input buffers, even in case they contain less than L elements.

The rest of the proof is only formula bashing to get the desired form.

First,  $M \in \Omega(L^2)$ , therefore  $\log M \geq 2 \cdot \log L$ . This leads to:

$$\log_{M/L} k = \frac{\log k}{\log M/L} = \frac{\log k}{\log M - \log L} \in \frac{\log k}{\Theta(\log M)} \subseteq \Theta(\log_M k). \tag{6.2}$$

Therefore we can exchange the base of the logarithm.

If  $k \in \Omega(L^2)$ , then similarly  $\log_M \frac{k}{L} = \log_M k - \log_M L = \Omega(\log_M k)$ . On the other hand, if  $k \in o(L^2)$ , then  $\frac{k}{L} \cdot \log_M k \in o(L \cdot \log_M L) \in o(k)$ , therefore the +k term dominates.

This together would allow us to write the result as  $\mathcal{O}(\frac{n}{L} \cdot \log_{M/L} \frac{k}{L} + k)$ . As n > k, we can replace k with n in an upper-bound estimate.

To sort the *n* elements, we need to split the input into  $\sqrt[3]{n}$  blocks, sort each of the blocks and merge them together using the  $\sqrt[3]{n}$ -funnel. This would give a recurrence:

$$T(n) = \sqrt[3]{n} \cdot T\left(n^{2/3}\right) + O\left(\frac{n}{L} \cdot \log_{M/L} \frac{n}{L} + \sqrt[3]{n}\right). \tag{6.3}$$

If the computation does not fit completely into the internal memory, the  $n \in \Omega(M) \subseteq \Omega(L^2)$ . In other words,  $L \in O(\sqrt{n})$ , therefore the n/L is larger than  $\sqrt[3]{n}$  and we can forget the  $\sqrt[3]{n}$  part for simplicity.

We consider the tasks of size  $\Theta(L^2)$  the leaves of recursion. Anything below fits into the internal memory and is therefore for free.

Such task can be read into the internal memory in  $\mathcal{O}(L)$  memory transfers and solved inside it, causing no more transfers. As there are  $\mathcal{O}(n/L^2)$  such tasks, the total cost over all of them is  $\mathcal{O}(n/L)$ .

The root of the recurrence dominates. Therefore the total cost is  $\mathcal{O}(\frac{n}{L} \cdot \log_{M/L} \frac{n}{L})$ .

To save some typing in the rest of the work, we'll use  $\operatorname{sort}(n)$  instead of the function  $\frac{n}{L} \cdot \log_{\frac{M}{L}} \frac{n}{L}$ .

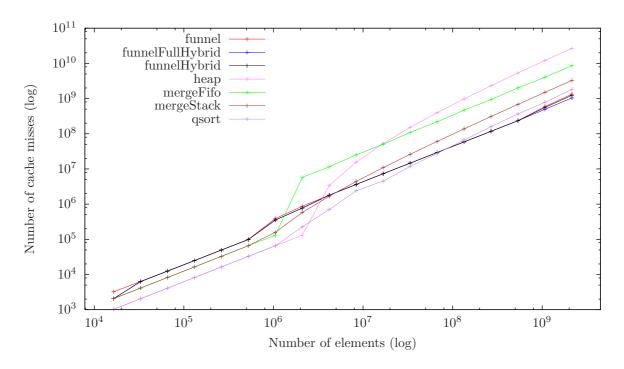

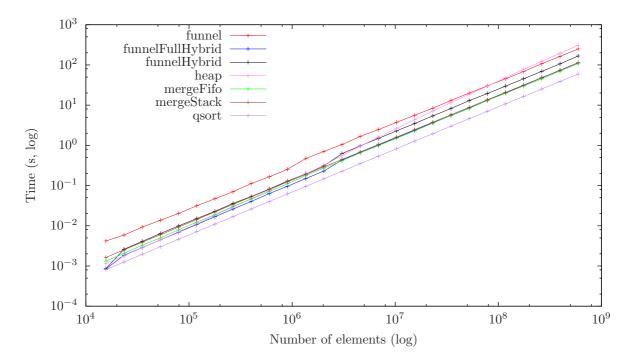

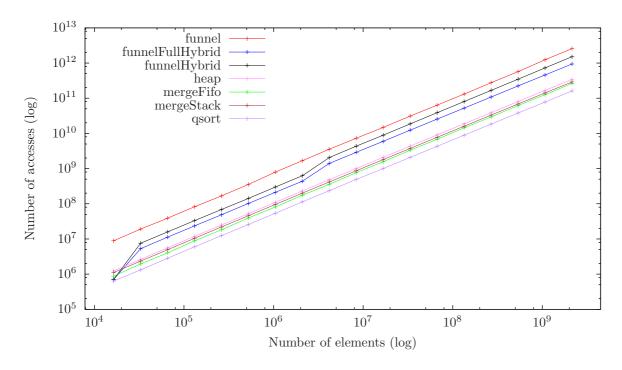

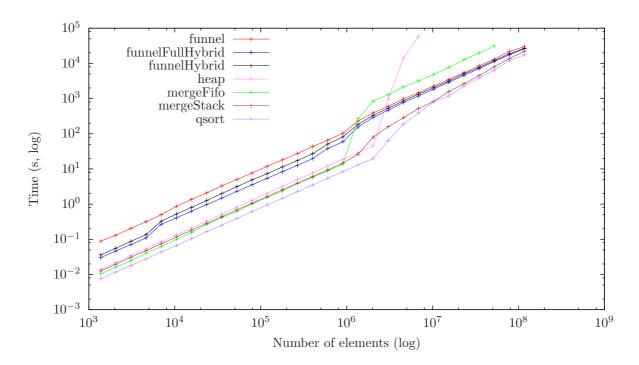

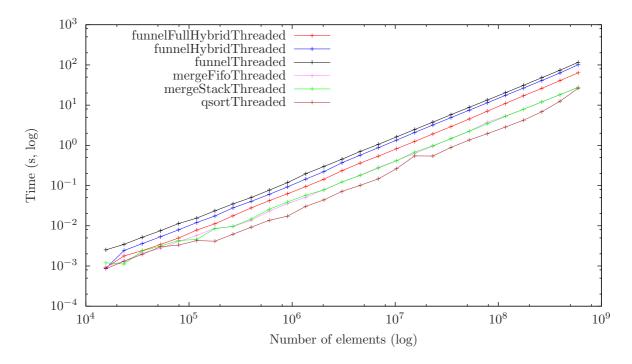

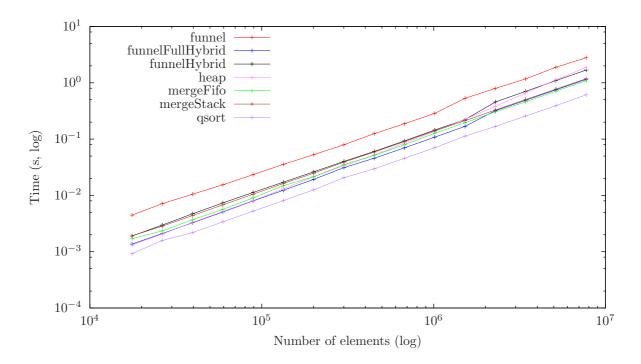

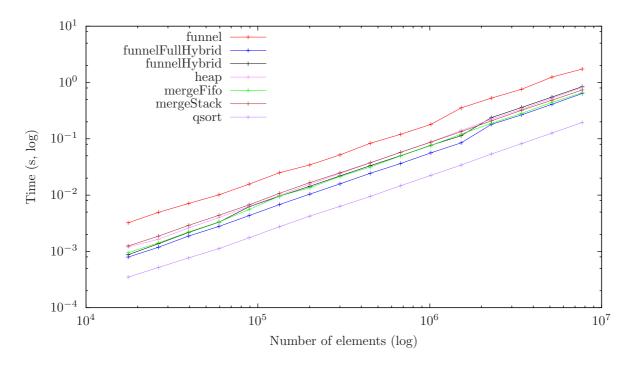

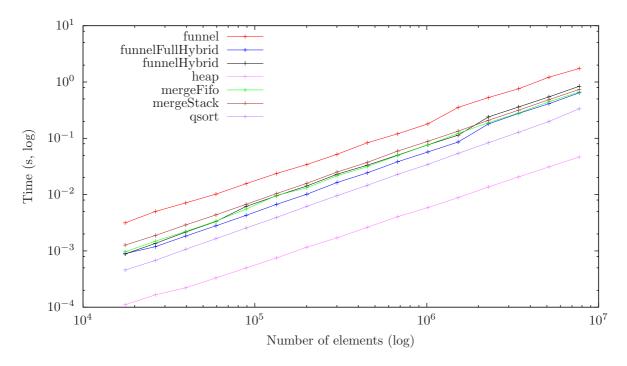

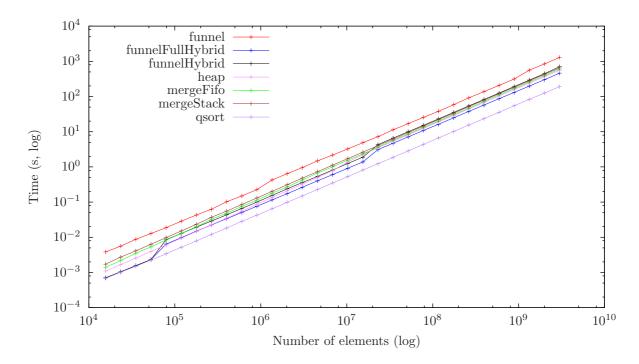

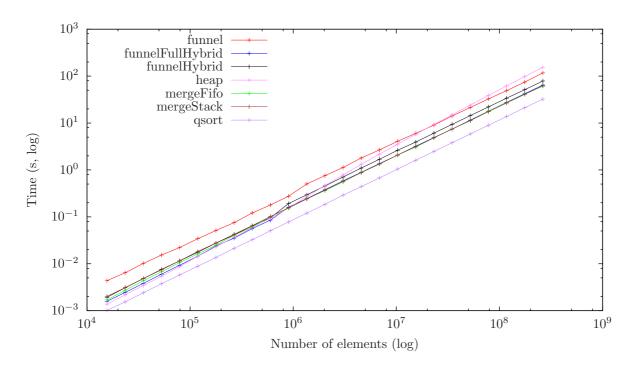

## 6.4 Experimental results

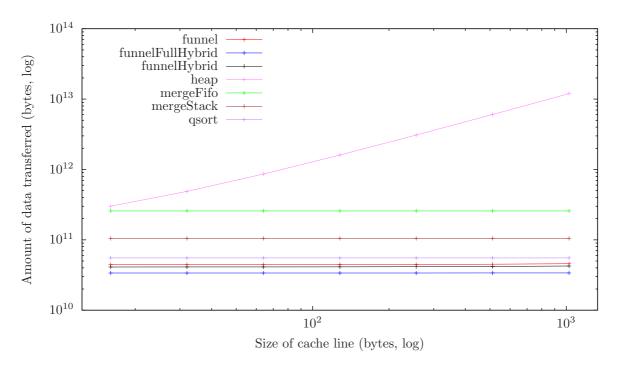

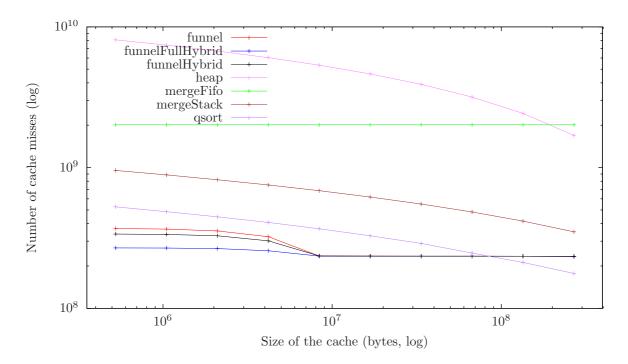

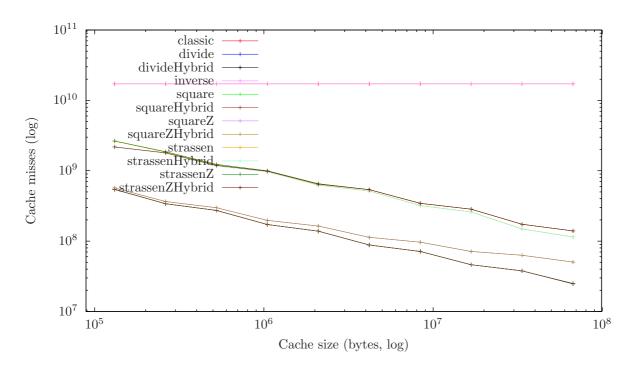

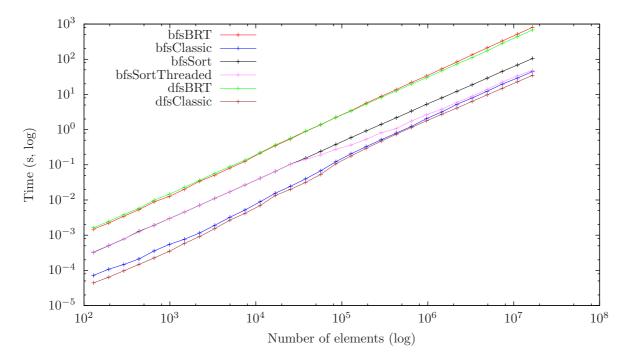

After having looked at the theory, let's examine the practice. The tested algorithms include:

- Both merge sorts.

- Funnel sort as described here.

- The well known heap sort with binary heap.